Friday, July 10, 2009

Divided by N state machine

Input is serial bit stream.

Eg: Say the state machine can detect "divided by 5" numbers.

I/P: 10101

O/P: 00110

Think in a generic manner(divided by N)

Gatesims

Friday, June 12, 2009

difference between conditional assignment and if else

c = check ? a : b;

and

if(check) c = a;

else c = b;

Monday, June 8, 2009

Highest # of ones or zeros

Eg:

IN : 001110110000

OUT: 0111111000

Constraints:

1) You are supposed to use only Multiplexers and DFFs for

your design. No external gates. To be specific, 1 4:1 Mux only.

2) Design should be optimized one.

3) Only one clock is available to you. And it is given that the

input is sampled at that clock rate only.

What is the FIFO Depth

a. 2000 samples

b. 1900 samples

c. 200 samples

d. 190 samples

# of boolean functions with ‘n’ inputs

Remove short length pulses

It is required to eliminate short length pulses from a sampled data. It means 0’s in continuous 1’s have to be made 1 & similarly 1’s in 0’s are to made 0’s as shown in the following example. Give the

Eg: I/P 0 1 0 0 1 1 0 1 1 0 0

O/P 0 0 0 0 0 1 1 1 1 1 0Monday, March 2, 2009

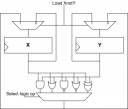

Swapping X & Y

X and Y are n-bit wide registers. In each clock cycle you can select a bit-wise basic operation between X and Y and store it to either X or Y, while the other register keeps its value.

The problem is to exchange the contents of X and Y. Describe the values of the “select logic op” and “load XnotY” signals for each clock cycle.

Thursday, February 26, 2009

Count the Number of 1's

Output: Number of 1's in the input

Available Components: Only Full Adders

Difficulty Level: Easy

Wednesday, February 25, 2009

Building XOR with alien gates only

There is a shortage of XOR gates. The only logic gates available are “X” and “Y”. The truth table of both components is presented below.

Build an XOR gate using these gates?

About the Digital-VLSI Blog

I am creating 4 labels for all the posts within this blog. All posts in this blog will be categorized as belonging to one among these.

They are

1. Clarify your Query

2. VLSI Interview Experiences

3. Digital VLSI Interview Questions

4. Question of the Day

Let me know if you feel there should be more categories or labels for the posts within this blog.